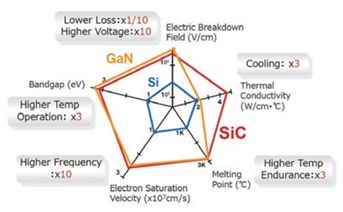

半导体产业的发展一共分三个阶段,第一代半导体材料是硅(Si),第二代半导体材料是以GaAs和SiGe为代表的微波器件,而现在最热门的是第三代半导体材料是宽禁带半导体材料GaN和SiC,相较前两代产品,性能优势显著并受到业内的广泛好评。第三代半导体具有高击穿电场、高饱和电子速度、高热导率、高电子密度、高迁移率等特点,因此也被业内誉为固态光源、电力电子、微波射频器件的“核芯”以及光电子和微电子等产业的“新发动机”。发展较好的宽禁带半导体主要是SiC和GaN,其中SiC的发展更早一些。

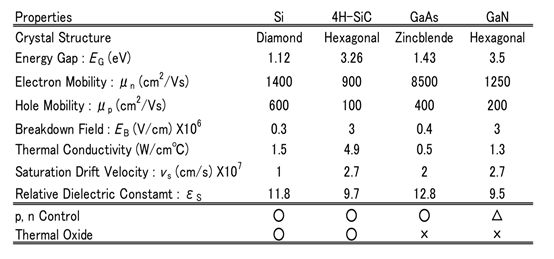

功率半导体围绕着硅(Si)发展了半个世纪,一直在BV和Ron之间博弈,也是一个功率器件最基本的门槛。这两个参数一个决定了器件的极限(BV)一个决定了器件的性能(Ron),这就如同鱼和熊掌不可兼得。而在BV的提升上面,主要考虑有源区(Active)和场区(Field),而Active区的击穿电压自然就是靠PN自己了,没其他办法,而场区也是最后器件电场线集中收敛的地方,这个区域的电场会很强,因此很容易在这里击穿,所以如何提高终止区的击穿电压成了硅基功率器件的重点,当然发展了这么多年最行之有效也是最成熟的方法就是保护环(Guard Ring)和场板(Field Plate)或者搭配来实现终止区的耗尽区宽度进而降低表面电场,使得击穿尽量发生于Active区的PN结。理论上只要这两道环设计的好,都能使得器件的击穿电压达到理想的PN结击穿电压。但是即便如此,受限与硅材料本身的特性,他的击穿电场也是要受限于他的禁带宽度(Eg)的,所以硅基的功率器件在1000V以上的应用时候就显得非常吃力,而且制造成本和可靠性等等都非常高,急需要寻找一种宽禁带半导体材料来获得更高的击穿临界电场以及电子迁移率,而目前这种材料就是SiC和GaN这两种材料。

话说新材料找到了,但是要全面取代硅基还是很困难啊,毕竟硅基器件的衬底和制造技术已经很成熟,价钱就可以秒杀你。所以在高压高功率的市场,一直存在着硅基功率器件和SiC/GaN的市场争夺战,其中硅基最得意的作品就是Si-IGBT和Super-Junction了。

继续讨论SiC和GaN吧。

1、衬底片生长(Crystal Growth):这是最基本的,就如同硅基在70年代一样,如果没有单晶衬底片,所有的制造业都是白谈,即使硅基的Si-ingot到目前为止全世界也只有5家可以拉单晶啊,可想而知多难!到了SiC和GaN那就更难了,几乎这就是主要制约这个行业发展的关键因素。

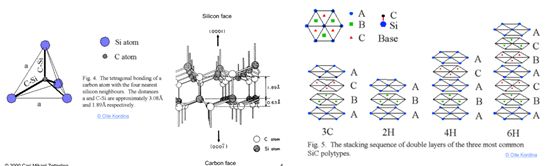

1)SiC制备:先说说SiC的结构吧,大家应该经常看到4H-SiC和6H-SiC,这是指他的堆叠层数。我从头讲起吧!首先,SiC都是第四主族的元素,所以每个Si和每个C刚好一一配对形成稳定的共价键结构,每个Si外面四个C,而每个C外面也是4个Si,也就是如下图的晶体结构。从结构上看,如果你正对Si面看下去的话,背面被挡住了一个C,所以你还能看到三个C,相同的情况,如果你正对着C面看下去,背面也被挡住一个Si,所以你还可以看到3个Si。因为一个C配一个Si,而刚刚说的不管从哪个原子看过去都可以看到三个另外原子,所以最好的晶体排布方式就是六边形结构,也就是书上说的六方最密堆积(HCP: Hexagonal Close Packing),如果不熟悉的话大家一定知道体心立方(BCC)和面心立方(FCC)吧,跟他差不多,也是一种晶体结构而已)。现在开始排布,第一层为A的球代表了双层Si和C的结构,那么下一层根据共价键的价键结构可以有两种分布,分别是B和C。而且A的下面一层只能是B或者C,不能是A自己,B和C也一样。所以这就有了多少种组合?ABA、ACBA、ACABA、ACBACBA,分别对应2H、3C、4H和6H了,而这个数字呢就是代表下一次重复前堆叠的层数而已,而目前SiC的功率半导体都是用4H-SiC或者6H-SiC,主要原因是他可以拉出比较大的wafer而已。

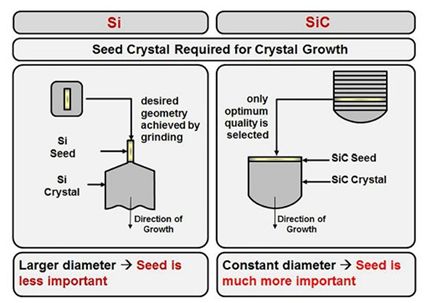

这个结构已经有了,关键怎么制造出来呢?和Silicon一样,CZ直拉的,但是条件非常非常苛刻。第一个是Seed,我们硅Ingot的拉单晶所需的seed很小,wafer的直径和seed大小无关,但是SiC的seed直径直接决定了final wafer的直径,所以seed必须很大。

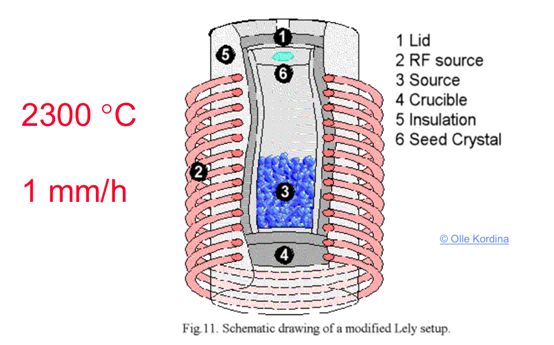

其次是反应条件,温度已经不是Silicon的1400C了,而是2300C,所以加热系统已经是RF coil,且坩埚替换成了石墨(graphite)。他其实是一种物理气相沉积(PVD),只是他不是Sputter的而是加热沸腾然后冷凝到seed表面形成的ingot而已。生长速率只有1mm/hour,所以可想而知SiC的价格多贵了吧,而且目前尺寸只能做6寸,主要是受wafer表面的温度均匀性限制,而且doping level没办法做高,如果要想用high doping的SiC衬底,必须要用CVD EPI的方式来重新生长(1400C~1600C, 3um/hour, SiH4+H2+CH4+C3H8, etc),而且doping的元素主要是Al和Boron为P型,而Nitrogen和Phos为N型。如果是离子注入(Ion Implant)的方式来doping的话,会引入晶格损伤,而这种损伤很难消除,必须要用高温离子注入(High Temperature Implanter: 700C)以及高温退火(1200C~1700C)才能缓解和消除,这就是process里面最大的挑战!

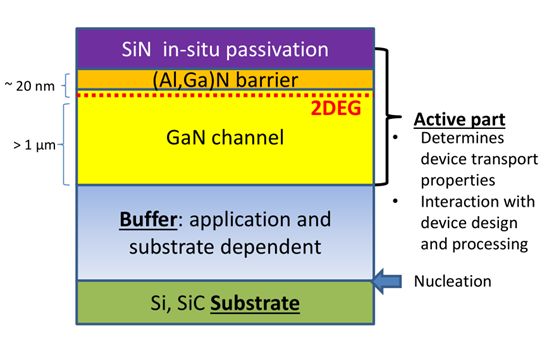

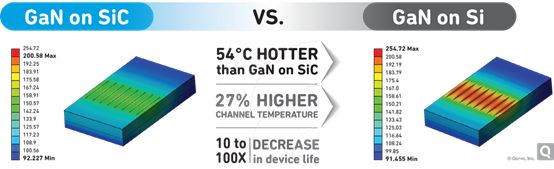

2) GaN衬底:GaN主要都是MOCVD或者分子束外延(MBE)在衬底上长一层GaN而已,但是对于衬底的选择很重要,如果是作为功率的switch器件,都是选择GaN-on-Si,如果是用作RF的话,就需要选择GaN-on-SiC,显然后者受衬底依耐比较大,仅限于6寸晶片。至于他是怎么外延的,为什么要有成核(neuclization)和buffer层等等,必须要先懂他的器件原理才能理解,后面讲器件的时候一起讲吧。

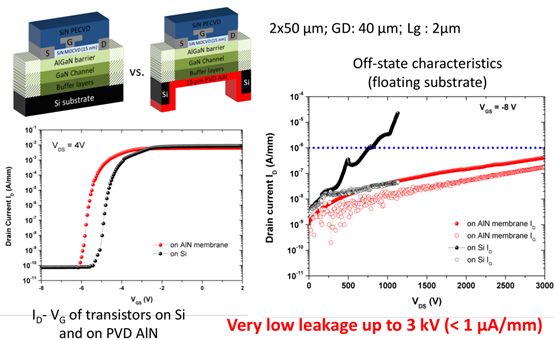

Si上的GaN已经证明了现有GaAs技术的原始功率密度仅为8倍,同时将效率提高到70%。GaN on Si性能现已与SiC衬底上更昂贵的GaN相匹配。而且在Si上使用GaN允许供应商转移到8寸晶圆厂达到cost down。在这里,CMOS工艺控制通常可以使线路产量高于98%。由于CMOS正在解决的终端市场数量极高,平衡产量和成本动态至关重要,如果能推到8寸,其cost可以降低10倍,而且产能足够。

2、器件工作原理:留着另起一个专题吧,太复杂了!这里只是买个伏笔吧。

1) SiC器件: SiC器件方面,主要跟Silicon结构差不多,也需要氧化和PN结等,还是Diode (FRD, SBD, etc), MOSFET, IGBT,等等。国际上SiC肖特基二极管(SBD)、金属氧化物半导体场效应晶体管(MOSFET)等均已实现量产,产品耐压范围600V-1700V,单芯片电流超过50A,并开发出了1200V/300A、1700V/225A的全SiC功率模块产品;实验室开发了10000V-15000V / 10A-20A的SiC MOSFET;并研发出了IGBT芯片样品,最高耐压水平已经超过20 kV量级。

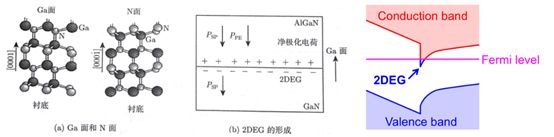

2)GaN器件:主要是靠异质结的极化产生压电效应(piezoelectric polarisation),最后在异质结交接处产生两维电子气 (2DEG: 2-D electron gas),而这个电子气的速度比普通的电子快2.7倍,所以速度很快,但同时他也是常开状态(耗尽型器件)。还有一些场板设计等等后面再说。所以这种器件的key在于异质结是否做的好?稍微有个晶格缺陷就挂了,搞来搞去还是衬底材料是重点啊!所以GaN的器件又叫HEMT: High Electron Mibility Transistro)

我们期待技术的成熟,当价格能降到硅器件的2~3倍,市场肯定会被SiC和GaN全面取代掉。尤其是2020年以后,全球普及EV汽车的时候,根据预测,直到2020年我们几乎有21%的年复合增长率。

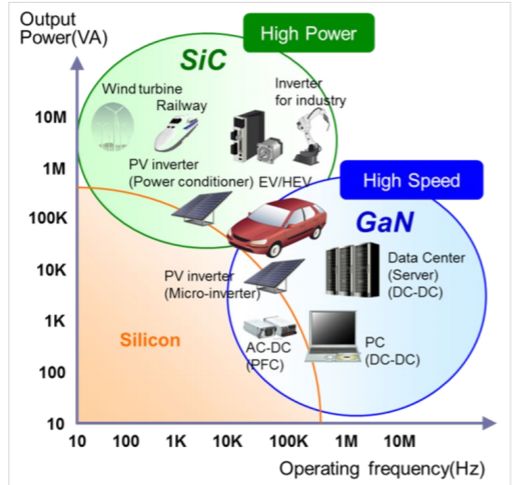

SiC和GaN都是宽禁带半导体材料,而且禁带宽度都几乎是Silicon的三倍,所以都非常适合功率器件,而且饱和载流子速度都几乎是硅的10倍,所以他们都非常适合做High frequency的RF器件。而从下面的对比可以看出SiC和GaN有一个很大很大的区别是导热系数,GaN和Silicon几乎差不多,而SiC超好,几乎是GaN和Si的三倍以上,这就决定了在高功率应用领域SiC肯定就占领了绝对统治地位,散热问题就解决了,而且抗高温。

所以在低功率和高频率的应用领域里,GaN就可以PK掉SiC了。在半导体器件里面用到的GaN都是在高温下(~1100C)通过MOCVD或者MBE(分子束外延)的方式来生长的,目前业界有两种衬底可供外延或MOCVD,一种是GaN-on-SiC,另一种是GaN-on-Silicon。前者以SiC为衬底的GaN主要应用于高功率和高频(high RF)领域,主要得益于SiC的高导热率以及低RF loss,但是受限于SiC的衬底只能限制在6寸,所以目前8寸还没有推广。而GaN-on-Si自然就比不上了,但是他便宜啊,而且可以做8寸,产能和成本都非常有竞争力,所以在5G消费类市场上应该很有竞争力有望全面取代硅基LDMOS。

除了GaN-on-Si和GaN-on-SiC,还有一种GaN-on-Sapphire (蓝宝石/Al2O3),衬底比较便宜而且能抗得住高温外延。但是蓝宝石衬底的导热性非常非常差,几乎是硅衬底的千分之一,而且他的晶格失配以及热膨胀系数也很大。而这些缺点似乎SiC都完胜,唯一的就是SiC太贵了。

首先来说说GaN晶体管的工作原理吧,我们都知道GaN是属于异质结 HEMT,所以他的工作离不开异质结(Heterojunction),不是硅基的PN结哦。这个异质结就是利用一种比GaN禁带宽度更高的AlGaN与GaN组合在一起,由于AlGaN和GaN的异质结存在两种极化效应:自发计划(RSP)和压电极化(RPE)。其中自发极化主要来自化合物半导体自己的原子核与最外层电子的库伦引力,由于N原子表面被吸附了很多的电子,因此库伦引力比较强,所以GaN结构的非对称的纤维锌矿GaN晶体结构引起的自发极化,而压电极化主要来自晶格失配的外部引力带来的极化电荷,正是由于这两种极化共同作用,所以在AlGaN和GaN的界面处产生极化静电荷。从而形成2DEG (两维电子气),其面电荷密度随着AlGaN里面Al含量的增大而增大,但是越大的Al会带来严重散射,从而造成电子迁移率下降,所以这是一个trade-off。一般情况Al:Ga的比例为3:7,电子密度可以达到1.7×1013cm-2,这几乎是其他Ⅲ-V族异质结器件的10倍。

有个小插曲,GaN的晶格有两个面,一个是Ga面,一个是N面,N面的接触电阻比较低,但是击穿电压小,所以一般功率器件都是用Ga面,而且Ga面具有更均匀,更平坦的异质结界面特性。

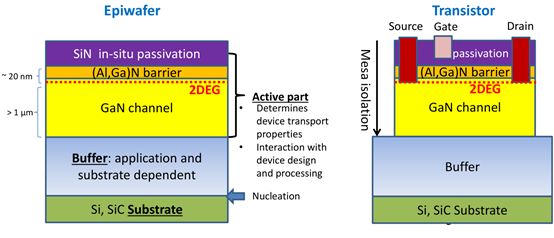

至此,我们应该知道GaN晶片必须至少有AlGaN和GaN两层外延,才能形成异质结构,其实还不够。在GaN的下面与衬底之间还需要一个Buffer Layer或者叫做Nucleation layer,其作用是防止产生界面缺陷导致界面电子气寿命下降。而在AlGaN上面还需要有一个In-situ Si3N4 Cap layer,这个很关键,他必须是MOCVD长完之后不出腔体直接长一层MOCVD的SiN,他是器件可靠性的关键,如果是后续process做的话很容易产生Interface charge,从而产生一个Gate到Drain的导电层而漏电。所以power GaN的外延至少是四层(LED的GaN更复杂哦)。

接下来,我们从器件的结构开始讲,然后对结构有了了解之后,再来讲Process flow吧,这是我一直采用的training方法。

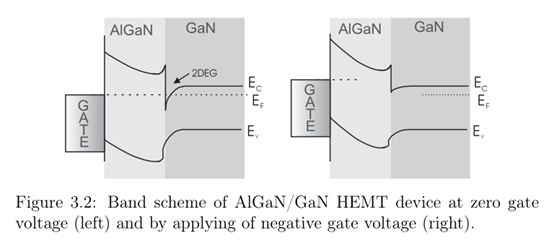

首先GaN HEMT器件的沟道2DEG在衬底制备的时候已经形成了,所以没有CMOS那么复杂还要长GOX和Poly Gate电极等等,所以对于GaN HEMT来讲,只要定义Gate控制电极,然后定义S/D区域,用Metal引出去就好。似乎非常简单!事实并非如此看似简单。首先说Gate,GaN HEMT的Gate控制原理是靠一个肖特基二极管控制的,HEMT是电压控制器件,栅极电压Vg可控制异质结势阱的深度,则可控制势阱中2-DEG的面密度,从而控制着器件的工作电流。如下图所示的能带图,左边是Gate偏压为0时候的情况,此时AlGaN和GaN已经弯曲形成了三角区域的2DEG,这个时候只要D/S之间有电势差就可以产生电流了。如果Gate加负电压,直观的理解是Gate下面的空间电荷区开始朝沟道下面和两边扩展,知道耗尽区碰到沟道2DEG,从而是沟道被夹断(pinched-off)。

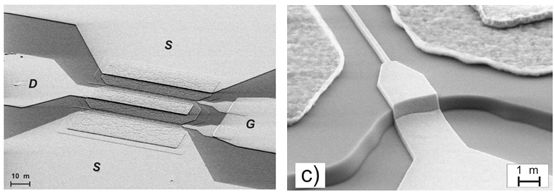

所以,GaN HEMT结构比较简单,就是S/D和Gate,而这三个端子都是只需要做一个Contact引个电极就可以了,然而process的难点就在这三个contact上。如果说器件驱动能力或者沟道的导通能力(电导率)完全由2DEG决定,而2DEG的密度完全有EPI决定,所以第一个难点是EPI,如果没有EPI的核心技术做GaN根本没什么意义,而第二部对于器件制造来讲有一些列难点,而这第一个难点就是Gate和Source/Drain的Contact。

对于Source/Drain来讲,他需要carrier或者conduct载流子赶快穿过S/D,所以他一定要是欧姆接触来减少conduction loss提高增益,做过CMOS的人都知道欧姆接触很容易哇,直接把Source/drain打高浓度掺杂,然后半导体禁带宽度变窄,降低势垒,最后发生隧穿不就实现了欧姆接触了吗?exactly!但是在GaN领域里面,就不行了。因为GaN是宽禁带啊,即使你降低那一点,还是没办法和金属隧穿啊(除非你掺杂浓度继续提高比Silicon高3~4倍,能实现吗?)。另外一个要注意的点是,如果你的欧姆接触处理的不好,器件的击穿电压(Vbr)又会受影响。所以一般有两种方法来提高欧姆接触,第一个是layout上,最好用圆形S/D的接触孔设计,如果contact是方形的话,边缘的电场分布不均匀会影响接触电阻,所以如果是方形的contact,就必须要用MESA(台面)工艺来隔离S/D,如果你不采用MESA隔离工艺的话,你也可以把contact设计成圆形(书上叫做“圆形传输线模型, C-TLM”)。还有一个解决欧姆接触的方法是从金属下手(估计学冶金的人比较懂吧~,感觉跟silicide差不多),用normal process沉积Ti/Al/Ni/Au四层金属,再在N2气氛中,经过700C以上的RTA退火,温度升高接触电阻会下降,这个温度下Al应该已经熔化了,就是为了Ti和Al在高温下充分发生固相反应,Al穿透Ti层到达GaN表面,同时高温下GaN里面的“N”又外扩散出来在界面出与Ti反应形成TiN,所以在GaN表面产生N空位作为施主,提高表面浓度有助于电子隧穿,形成好的欧姆接触。那么Ni和Au有什么作用?呵呵。这又复杂了,有没有注意整个过程感觉Ti和N很重要,实际上Al没什么作用对吧,实际上Al的作用是防止Ga外扩散跑出来,可是铝又很容易被氧化,所以需要一层金(Au)来保护,可是金又和铝容易互扩散,而且Au一旦进入到衬底,那整个半导体就废了,所以必须要在金下面铺一层Ni作用Barrier,是不是很麻烦?为什么不直接用TiN改在Al上面不就完事了吗?TiN的接触电阻太大了,对于GaN的RF/mW器件来讲,我们不允许任何高阻抗出现在contact里,所以我们必须要把contact电阻降低到理论的E-6~E-7 ohm.cm2。

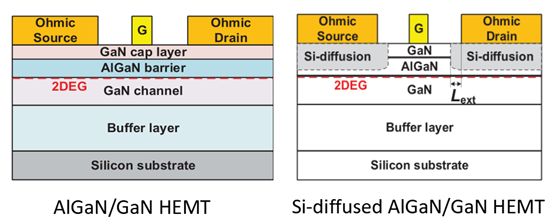

好了,刚刚大家有没有注意到Al在高温下已经熔化了,那么铝其实很容易穿过Ti进入GaN了,就出现了Metal Spiking问题,这样又出现了一个体内的SBD接触,改变了buffer区AlGaN的电场,会产生早期击穿,这可是可靠性问题。所以为了解决这个问题,可以在Source/Drain区域掺杂Silicon元素来保住这些spikes,通常就把这个silicon doping的区域做的比contact稍微大一点(Lext),这样进一步降低contact边缘的电场线强度,提升击穿电压。

接下来,我们讲栅极(gate)的接触孔,我们的栅极是肖特基接触,是不是无比麻烦,这就注定了栅极contact以及metal没办法和Source/Drain一起做了。所以必须要分开做。先说肖特基接触的重要性吧,这个金半接触的势垒ΦB直接决定了AlGaN的耗尽层宽度间接影响了2DEG的密度,而且和CMOS一样,他也是低频噪声的主要来源,亚阈值特性也是直接受栅极影响的。还有一个和CMOS不一样的是,GaN HEMT晶体管的最大工作电压和功率,完全是由Gate肖特基二极管的反向击穿电压决定的。一般情况下,类似我们CMOS的Gate,我们总希望我们的gate能够很好的控制channel,以此类推,我们希望我们的耗尽区尽快碰到2DEG的channel,可是我们的AlGaN非常厚,所以我们可以采用Recess蚀刻的方式来让他们的SBD接触不要在表面,而是在体内,这样gm就大了,fT和fMax就被提升了。但是这个AlGaN的recess etch又带来了挑战,他和MESA Etch还不一样,这个很care表面粗糙度以及corner电场,一般是ICP-RIE蚀刻采用Cl2/Ar气体,其GaN和AlGaN的选择比可以做到1:9,而且对于表面粗糙度的bonbardment的key factor是压力。 还有Gate金属怎么选择的问题?再一次回到SBD的理论,SBD的势垒高度有两个影响因素,一个是界面的钉扎效应(pinning effect),一个是金属的功函数和半导体的亲合能之差的能级决定的,而在宽禁带半导体中,钉扎效应所占比例非常小,所以几乎由金半接触势垒决定,这样的话我们可以选择Au、Pt (~1eV)、Ni (0.66~1eV)。但是除了势垒高度,还要考虑side-effect,那就是漏电和热稳定性(300~600C),这样最后只有Au和Ni了。所以Gate金属都是由Ni和Au组成的(Ni用来做黏附层,Au用来做整流SBD,其功函数是5.1eV)。

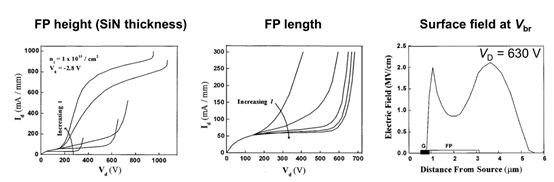

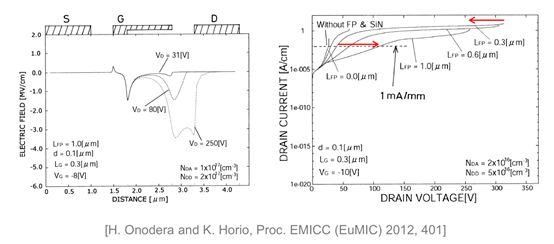

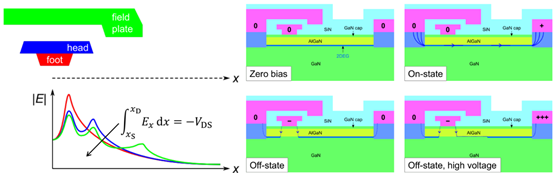

好了,栅极的SBD结构就讲完了,现在就是要如何优化结构,如果按照常规的设计,那么在Gate末端靠近Drain那一边的表面电场是最强的,所以需要有一个栅极场板设计(Gate Field Plate),有点类似LDMOS的场板。另外,由于我们Gate的SBD很怕漏电,而这个漏电也有可能来自于表面电荷或者后面的charging等等,所以一般设计可以考虑用Source Metal给Gate做一个接地的shielding (只是他不是在欧姆接触的时候做的,而是在PAD Metal的时候做的!),进一步降低Gate边缘表面电场。这个场板的设计对BV和寄生电容以及电荷碰撞以及迁移率都有影响,因此设计window必须要well charaterize (S. Karmalkar and U. K. Mishra, Trans. Elec. Dev. 48 (8), 1515 (2001))。

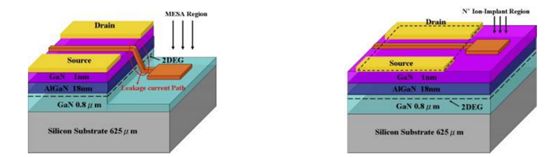

所以最后的结构就是如下图的样子,从图中可以看出In-situ SiN Cap或者passivation layer对器件的重要性非常高,直接决定了Gate漏电,器件击穿,可靠性等等,主要就是他容易引入在AlGaN和SiN界面上引入表面电荷,从而改变2DEG电荷分布以及Gate和Drain之间的电场等。

最后再讲一个Device Isolation,一个是MESA的台面结构,一个是离子注入的方式PN结隔离,前者主要是有台阶,而且侧边的2DEG会碰到Gate Metal,造成漏电和BV降低,所以离子注入隔离是比较不错的方法,而且表面平坦可靠性和金属台阶覆盖性都比较好。